超大规模集成电路(VLSI,Very-Large-Scale Integration)是现代电子信息技术和数字社会的基石,它将数以亿计乃至数十亿计的晶体管集成在单一芯片上,实现了前所未有的计算能力、能效比和功能密度。VLSI的设计与分析是一个高度复杂、多学科交叉的工程领域,涉及从系统架构到物理实现的完整流程。

一、VLSI设计的核心挑战

VLSI设计的首要挑战在于“规模”与“约束”的平衡。随着晶体管尺寸进入纳米尺度,设计者不仅要管理海量组件的逻辑功能,还必须应对一系列物理极限问题:

- 功耗与散热:集成度的提升导致功率密度急剧增加,功耗(特别是静态功耗)和散热成为制约性能的瓶颈。低功耗设计贯穿始终。

- 时序收敛与信号完整性:工作频率的提升使得时序裕度变小,互连线延迟、时钟偏移、串扰噪声等问题严重影响电路稳定性和性能。

- 制造工艺变异:在先进工艺节点下,制造过程中的微观变异会导致芯片性能、功耗的偏差,设计必须具有足够的鲁棒性。

- 设计复杂度与成本:设计一款先进VLSI芯片的研发成本和时间成本极高,需要高效的电子设计自动化(EDA)工具和设计方法学支撑。

二、VLSI设计的主要流程

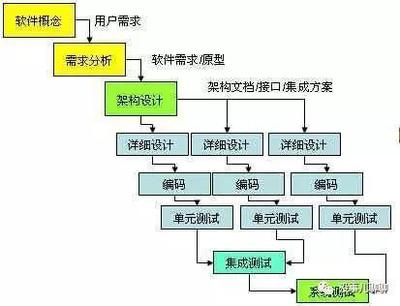

典型的VLSI设计流程是一个自上而下、逐层细化的过程,主要包括以下几个阶段:

- 系统架构与规格定义:根据应用需求(如处理器、通信芯片、AI加速器)确定芯片的整体功能、性能指标、功耗预算和接口协议。

- 算法与硬件协同设计:对于特定功能(如图像处理、信号解码),进行算法优化并将其映射到高效的硬件架构上,平衡速度、面积和功耗。

- 前端设计(逻辑设计):

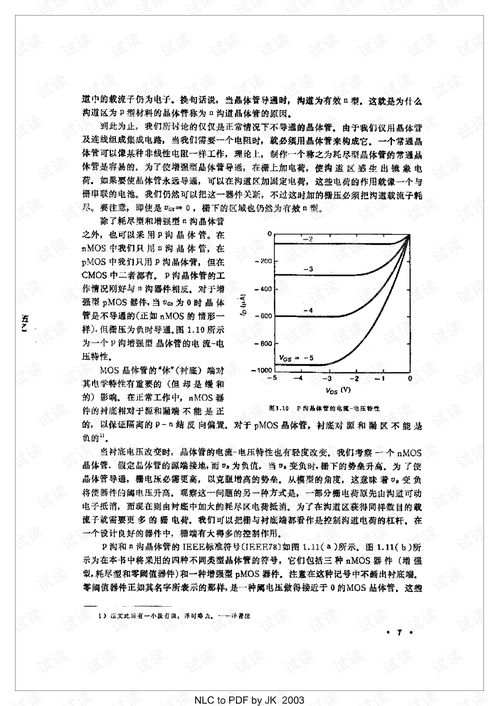

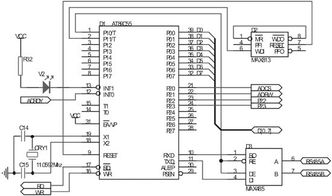

- 寄存器传输级(RTL)设计:使用硬件描述语言(如Verilog, VHDL)描述芯片各模块的数字逻辑功能。

- 功能验证:通过仿真、形式验证等方法,确保RTL代码的行为符合规格要求。

- 逻辑综合:使用EDA工具将RTL代码映射到特定工艺库的标准单元和基本模块,生成门级网表。

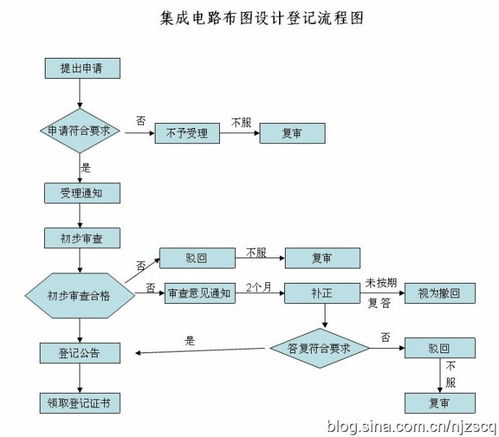

- 后端设计(物理设计):

- 布局规划:规划芯片核心区域、模块位置、I/O引脚和供电网络。

- 布局与布线:确定标准单元和宏模块的具体位置,并根据电气连接关系进行金属连线。

- 时序分析与收敛:在考虑实际布线延迟后,进行静态时序分析(STA),确保在所有条件下满足时序要求,若不满足则需反复优化。

- 物理验证:进行设计规则检查(DRC)、版图与电路图一致性检查(LVS)以及电气规则检查(ERC),确保版图符合制造工艺要求且功能正确。

- 签核与流片:完成所有验证后,生成最终的GDSII版图文件交付给晶圆厂进行制造。

三、VLSI分析的关键技术

在整个设计流程中,深入的分析是保证芯片质量的关键:

- 时序分析:静态时序分析(STA)是验证电路速度的基石,它检查所有路径在最坏情况下的延迟。

- 功耗分析:分为动态功耗(开关活动引起)和静态功耗(漏电流引起)分析。工具会模拟电路活动,精确估算各模块和整体的功耗。

- 信号完整性分析:分析串扰、电源地噪声、电迁移、IR压降等效应,确保信号在高速传输下的可靠性。

- 可测试性设计与分析:通过插入扫描链、内建自测试(BIST)等结构,提高制造后芯片的故障覆盖率和测试效率。

- 可靠性分析:评估芯片在热载流子注入、负偏置温度不稳定性等效应下的长期寿命。

四、前沿趋势与展望

VLSI设计领域正随着应用需求和技术发展而快速演进:

- 异构集成与Chiplet:通过将不同工艺、功能的芯粒(Chiplet)进行先进封装集成,突破单芯片的规模与成本限制。

- 领域专用架构:针对人工智能、自动驾驶等特定领域,设计高度定制化的硬件架构以获得极致能效。

- EDA与AI的融合:机器学习技术正被广泛应用于布局布线、验证、功耗优化等环节,以提升设计自动化水平和质量。

- 新器件与新材料:碳纳米管、二维材料、硅光子等新兴技术为后摩尔时代的集成电路带来新的可能性。

超大规模集成电路的设计与分析是一门将抽象算法转化为物理现实的精妙艺术与严谨科学。它要求工程师不仅精通电子学与计算机科学,还需深刻理解材料、物理和制造工艺。面对持续增长的性能需求和日益严峻的物理挑战,VLSI设计方法论与工具的创新,将继续驱动整个信息产业向前发展。