在北京理工大学《集成电路设计实践一》这门重要的专业实践课程中,VHDL(VHSIC Hardware Description Language,超高速集成电路硬件描述语言)的掌握是连接理论知识与实际硬件设计的核心桥梁。它不仅是描述数字系统行为的软件工具,更是实现从概念到芯片的关键开发手段。

VHDL作为一种强大的硬件描述语言,在课程中扮演着多重角色。它允许学生使用高级的、类似于软件编程的语法,来精确描述复杂的数字逻辑电路,如寄存器、状态机、算术逻辑单元等。与直接绘制电路图相比,VHDL提供了更高的抽象层次和灵活性,便于进行大规模、模块化的设计。在“软件开发”的语境下,这里的“软件”特指用于描述、模拟和综合硬件电路的代码与开发环境。学生通过编写VHDL代码,实质上是在进行一种特殊的软件开发——其最终产物是硬件电路的结构或行为。

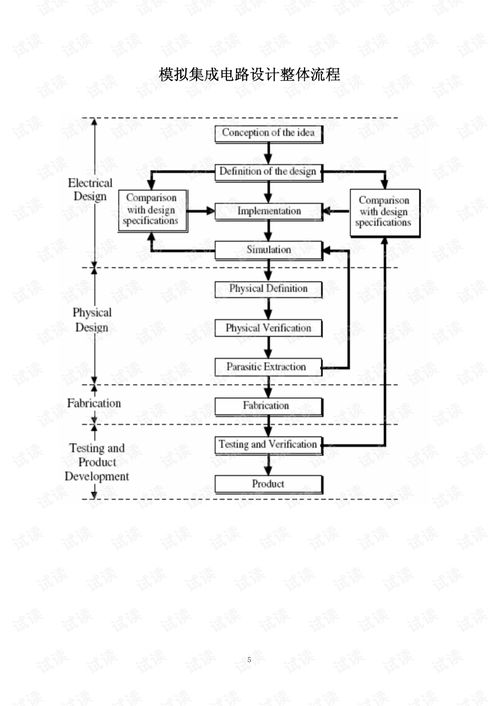

课程实践通常围绕典型的数字系统设计流程展开:

- 设计输入:学生使用集成开发环境(如Intel Quartus Prime、Xilinx ISE/Vivado),将电路构思转化为结构清晰、符合规范的VHDL代码。这要求熟练掌握VHDL的基本结构(实体、结构体)、数据类型、并行语句和顺序语句。

- 功能仿真:编写测试平台(Testbench),对设计模块施加激励信号,通过软件仿真验证其逻辑功能的正确性。这个阶段完全在软件环境中进行,是排查逻辑错误的关键,深刻体现了“软件开发”中的调试与验证思想。

- 综合与实现:利用综合工具,将行为级的VHDL描述“编译”和优化成目标工艺(如FPGA)对应的门级网表。这个过程将抽象的代码映射为具体的硬件资源,是硬件设计软件化的核心体现。

- 时序分析与下载测试:对综合后的设计进行时序分析,确保满足时钟频率要求,最终将生成的配置文件下载到FPGA开发板进行实物验证。

要成功掌握本课程中的VHDL软件开发,学生需注重以下几点:

- 理解硬件思维:牢记VHDL描述的是并行执行的硬件电路,这与传统串行执行的软件编程有本质区别。清晰的硬件结构观念是写出高效、可综合代码的基础。

- 熟练核心语法与设计模式:深入理解进程、信号与变量的区别,掌握有限状态机、数据路径等经典结构的VHDL实现方法。

- 善用开发工具:熟悉IDE的工程管理、仿真调试、综合约束等各项功能,能高效利用工具定位和解决问题。

- 实践驱动学习:通过完成课程中从简单组合电路到复杂数字系统(如小型CPU、通信接口)的一系列设计项目,在实践中巩固和深化对VHDL语言的理解与应用能力。

在北京理工大学《集成电路设计实践一》中,VHDL语言的掌握绝非简单的编程学习,而是培养硬件系统级设计能力、贯通“软硬件界面”的核心实践。熟练运用VHDL进行“软件开发”,是学生迈向专业集成电路设计工程师道路上的坚实一步。